|

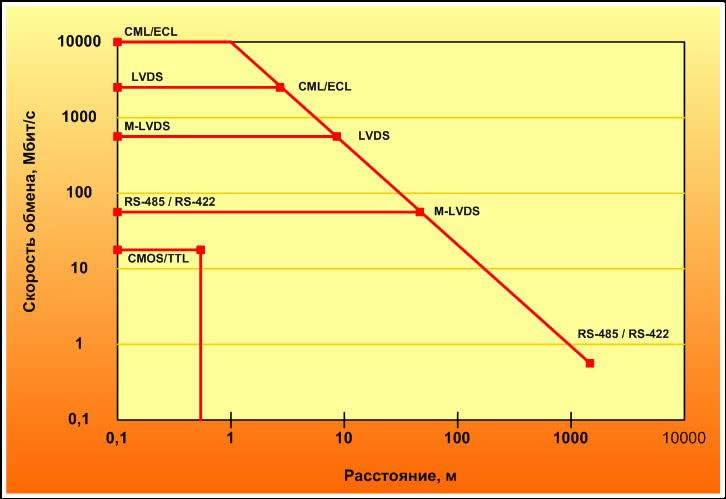

Стандарт LVDS позволяет выпускать разнообразные решения дифференциального интерфейса, способного поддерживать скорость передачи до 1 Гбит/с на расстояния до 10 м. LVDS означает передачу информации дифференциальными сигналами малых напряжений (до 350 мВ) по двум линиям печатной платы или сбалансированному кабелю. |

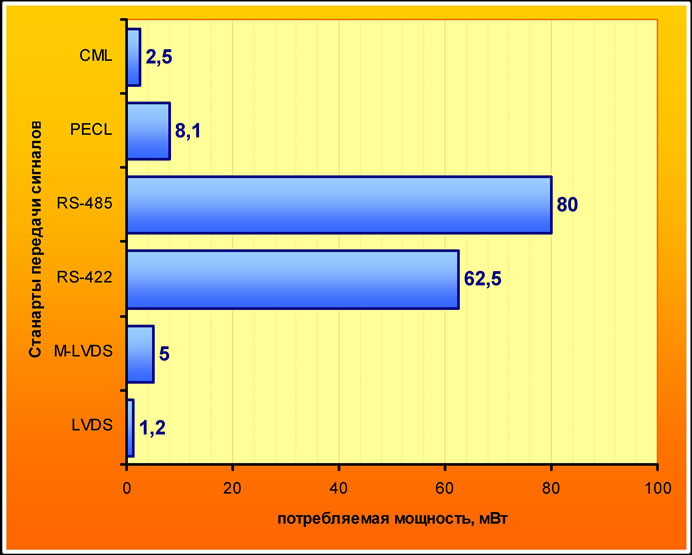

В сравнении с обычными однопроводными системами дифференциальный метод благодаря ослаблению синфазного сигнала обеспечивает лучшую помехоустойчивость и, соответственно, работу при меньших значениях напряжения, меньшую потребляемую мощность, меньшую чувствительность к электромагнитным помехам и большую скорость передачи.

На ОАО «Интеграл» проведены разработка и освоение цифро-аналоговых ИМС двойного назначения счетверенного линейного передатчика 5560ИН1Т и счетверенного линейного приемника 5560ИН2Т последовательных данных стандарта LVDS.

Микросхемы работоспособны в диапазонах напряжений питания от 3 до 3,6 В и температуры от -60 до 125°C. Входы, выходы микросхем 5560ИН1Т, 5560ИН2Т устойчивы к воздействию статического электричества на уровне не менее 2000 В. Электрическая схема защиты от статического электричества разработана на основе закрытого биполярного n-p-n транзистора с типовым пробивным напряжением около 7 В.

Входы данных и управления микросхем передатчика, приемника, а в третьем состоянии выходы микросхемы передатчика допускают режим превышения напряжения выше напряжения питания. На входы передатчика приходят сигналы с уровнями КМОП/ТТЛ. В цифровой части схемы происходит расщепление сигнала на прямой и инверсный. В аналоговой части схемы между прямым и инверсным выходами передатчика формируются дифференциальные сигналы, соответствующие уровням стандарта LVDS.

На прямой и инверсный входы приемника приходят дифференциальные сигналы стандарта LVDS.

В аналоговой части схемы на основе двухкаскадного дифференциального усилителя происходит детектирование сигнала и его преобразование в униполярный. На выходе приемника формируется сигнал с уровнями напряжения, совместимыми с уровнями КМОП/ТТЛ.

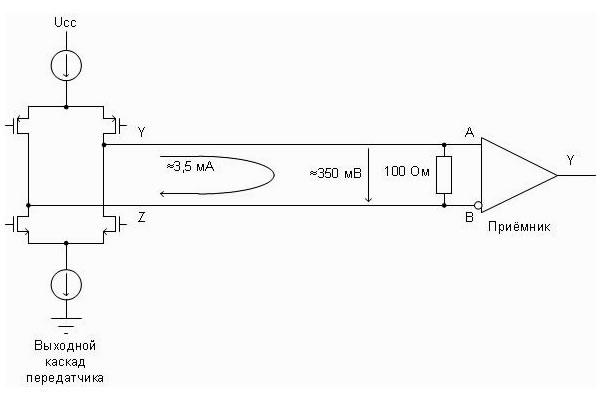

Схема сопряжения передатчика и приемника для систем связи типа «точка-точка» показана на рис.1.

|

Схема сопряжения «точка-точка» передатчика и приемника стандарта LVDS. |

В линии между прямым и инверсным входами приемника в непосредственной близости к приемнику (насколько это возможно) подключается согласующий терминальный резистор величиной 100 Ом. При типовом выходном токе передатчика равном 3,5 мА в линии формируется дифференциальное напряжение около 350 мВ, которое детектируется приемником, при этом, в связи с высоким сопротивлением приемника, его влияние на согласующий резистор не принимается во внимание.

|

Технические характеристики LVDS-интерфейса: - скорость передачи информации – 400 Мбит/с; - задержка распространения сигнала передатчика – 1,7 нс; - задержка распространения сигнала приемника – 2,1 нс; - протяженность линии 10м; - дифференциальная форма сигнала; - режим пониженного энергопотребления; - лучшие показатели из всех существующих интерфейсов по быстродействию и рассеиваемой мощности. |

В случае изменения направления тока в линии в режиме переключения изменяется полярность напряжения на нагрузочном резисторе, что позволяет различать состояния логического нуля и логической единицы.

ЗАО «РОССПЕЦПОСТАВКА»

Россия, 125212, Москва,

Кронштадтский бул., 7А, стр. 1

Тел./факс: +7 (495) 780-3686, 781-21-82